CoWoS封裝技術:為未來科技帶來的革命在當今科技飛速發展的時代

文/ 李品翰 編/ 謝明翰

一、前言

自從摩爾定律被提出以來,半導體技術一直在快速發展。摩爾定律指出,積體電路上可容納的晶片數量每隔18至24個月便會翻倍,但隨著製程技術的進步,單個晶片上的元件數量也不斷增加,這帶來了許多挑戰,包括散熱、功耗和連接等方面的問題。為了應對這些挑戰而發展出3D IC (Integrated Circuit, 積體電路) 的製程技術,3D IC是一種將多個電晶體在垂直方向做堆疊,以得到更高的等效元件密度和效能。為了迎合3D IC的需求,3D封裝技術應運而生,其中CoWoS (Chip-on-Wafer-on-Substrate)技術就是其中的一個典型代表。CoWoS是一項讓半導體晶片更加高效、可靠地運行的關鍵技術,今天我們將深入探討這一技術的原理、應用和未來發展。

二、什麼是CoWoS技術?

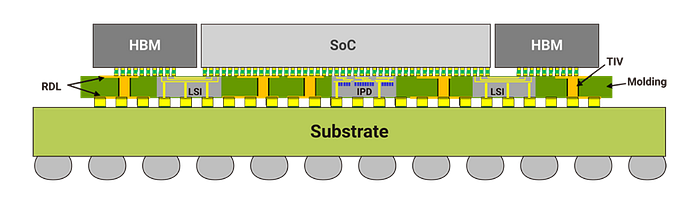

CoWoS封裝技術的全稱是Chip-on-Wafer-on-Substrate,顧名思義其結構為「晶片-晶圓-基板」。這種封裝技術是一種先進的三維積體封裝技術,通過將多個半導體晶片堆疊在一起,使它們可以在同一個封裝基板上進行連接和運行。與傳統的二維封裝技術相比,CoWoS技術具有更高的密度、更低的功耗和更快的速度。這使得晶片之間的連接更加緊密、更短,從而實現了更高的集成度和更小的封裝尺寸。與此同時,CoWoS技術還可以實現更低的功耗和更高的性能,這是因為晶片之間的連接距離更短,信號傳輸速度更快,功耗更低。此外,由於CoWoS技術採用了先進的封裝和連接技術,因此具有更高的可靠性和更長的使用壽命。

製程

1. 晶片堆疊

CoWoS技術的第一步是將多個半導體晶片堆疊在一起,形成一個稱為「晶片-晶圓-晶片」(Chip-on-Wafer)的結構。這些晶片可以來自不同的製造過程,具有不同的功能,例如處理器、記憶體或其他特定功能的晶片。

2. 封裝基板

在晶片堆疊完成後,需要準備一個稱為封裝基板的基板。封裝基板通常由玻璃纖維、硬質膠或其他適當的材料製成,具有良好的機械強度和導熱性能。

3. 連接

這個過程涉及將晶片堆疊的頂部晶片通過微細的連接線連接到封裝基板上。這些連接線通常是極細的金屬線或導體,其直徑僅幾個微米,可以在高精度的環境下製造。

4. 高精度定位和封裝

一旦連接完成,封裝基板需要經過高精度的定位和封裝過程。這個過程通常使用先進的自動化設備來實現,確保晶片的位置和連接線的準確性。

5. 封裝完成

當封裝基板上的所有晶片都被定位和連接,封裝過程就完成了。封裝完成後,可以通過各種封裝技術(如Ball Grid Array)將封裝基板連接到主板或其他電子設備上,從而實現整個系統的運行。

三、CoWoS技術的應用範圍和前景

- 高速運算:

CoWoS技術可用於高性能運算領域,例如數據中心、人工智能和機器學習應用中。通過將多個處理器、內存和其他功能單元集成在一起,可以實現更高的計算密度和更高的性能。

2.圖形處理:

在圖形處理器(GPU)和視覺處理器(VPU)等領域,CoWoS技術可以用於實現更高性能和更高功效的處理器。堆疊多個處理器、存儲器和其他功能單元可以提高圖形處理和視覺處理任務的性能。

3.網絡和通信:

在網絡設備和通信系統中,CoWoS技術可以用於實現更高的帶寬和更低的延遲。通過集成多個處理器、網絡接口和其他功能單元,可以實現更高的網絡吞吐量和更快的數據傳輸速度。

4.汽車電子:

在汽車電子系統中,CoWoS技術可以用於實現更高的性能、更低的功耗和更小的尺寸。

四、結語

CoWoS封裝技術代表了當今半導體封裝領域的最新進展之一,它為我們提供了一種強大的工具,可以實現更高效、更可靠的電子設備。通過將多個晶片堆疊在一起並進行微細的連接,CoWoS技術不僅提高了設備的性能和功能,同時也為未來科技的發展開啟了新的可能性。隨著人工智慧、物聯網、高性能計算等領域的持續發展,CoWoS技術將扮演著越來越重要的角色。它不僅為我們的日常生活帶來了便利,同時也推動著整個科技產業的進步。然而,我們也要意識到,CoWoS技術還面臨著一些挑戰,如散熱問題、製造成本等,需要通過不斷的研究和創新來解決。在未來,我們可以期待著CoWoS技術在更廣泛的領域得到應用,並為人類社會的發展和進步做出更大的貢獻。與此同時,我們也應該持續關注CoWoS技術的發展,並為其創新提供支持,以滿足人類對更高性能、更可靠電子設備的不斷需求。總之,CoWoS封裝技術代表著科技領域的前瞻性,它將為我們的未來帶來更多的可能性和創新。讓我們共同期待著CoWoS技術在未來的發展中取得更加輝煌的成就!

參考資料 :

[1] Wang, H.; Ma, J.; Yang, Y.; Gong, M.; Wang, Q. A Review of System-in-Package Technologies: Application and Reliability of Advanced Packaging. Micromachines 2023, 14, 1149. https://doi.org/ 10.3390/mi14061149.

[2] Y. -C. Hu et al., “CoWoS Architecture Evolution for Next Generation HPC on 2.5D System in Package,” 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 2023, pp. 1022–1026, doi: 10.1109/ECTC51909.2023.00174.

[3] R. Lu, Y. -C. Chuang, J. -L. Wu and J. He, “Reliability Challenges from 2.5D to 3DIC in Advanced Package Development,” 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2023, pp. 1–4, doi: 10.1109/IRPS48203.2023.10117647.